University of Global Village (UGV), Barishal

Department of Electrical And Electronics Engineering

## EEE 0714-2103 Electronics – 2

### **Course Content**

Prepared By : Dr. Mostafa Zaman Chowdhury Professor Dept of EEE, KUET

Edited By : Abdul Hai Utsho Lecturer Dept of EEE, UGV

### **Electronics-II**

### **Basic Course Information:**

- Course Title : Electronics 2

- ✤ Course Code: EEE 0714 2103

- \* CIE Marks: 90

- ✤ SEE Marks: 60

- Exam Hours: 2 hours (Mid term Examination)

3 hours (Semester End Examination)

- ✤ Semester: 3<sup>rd</sup> Semester

- Academic Session: Winter 2025

### **Electronics-II**

#### **Assessment Pattern:**

#### **CIE – Continuous Internal Evaluation (90 Marks)**

| Bloom's<br>Category Marks<br>(out of 90) | Mid Term (45) | Assignment (15) | Quiz (15) | Attendance &<br>External |

|------------------------------------------|---------------|-----------------|-----------|--------------------------|

| Remember                                 | 05            |                 | 05        |                          |

| Understand                               | 05            | 05              | 05        |                          |

| Apply                                    | 10            |                 | 05        | 15                       |

| Analyze                                  | 10            |                 |           |                          |

| Evaluate                                 | 10            |                 |           |                          |

| Create                                   | 05            | 05              |           |                          |

### **Electronics-II**

#### **Assessment Pattern:**

**SEE – Semester End Examination (60 Marks)**

| Bloom's        | Final Examination |

|----------------|-------------------|

| Category Marks | Term (60)         |

| (out of 90)    |                   |

| Remember       | 15                |

| Understand     | 10                |

| Apply          | 10                |

| Analyze        | 10                |

| Evaluate       | 10                |

| Create         | 05                |

### **Course Learning Outcome (CLO's):**

| CLO1 | Explain op amp structure. Describe the types of OPAMP                                                                                                            |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLO2 | Explain UJT structure and operation Will be able to explain OPAMP (operational amplifier) and its applications.                                                  |  |  |  |

|      |                                                                                                                                                                  |  |  |  |

| CLO3 | Explain the gain of Op Amp applications                                                                                                                          |  |  |  |

| CLO4 | Explains FET structure and operation. Translates the properties of n-channel and p- channel FET Calculates current and voltage of FET under the DC sources.      |  |  |  |

| CLO5 | Describes equivalent circuits of FET. Calculates current, voltage, and gain of FET under the Ac sources Will be able to explain the p-npn materials and devices. |  |  |  |

### **Course Rationales:**

This course introduces the advanced concepts of Electronics to the students. This course is required to understand and implement the advanced electronic circuits such as operational amplifiers, feedback amplifiers, frequency response, active filter etc. with the help of various problem solving.

### **Course Objectives**

This course has been designed for the students.

- 1. To learn and understand the different applications of operational amplifiers, feedback amplifiers and power amplifier circuits.

- 2. Analyzing BJT and FET AC operation.

- 3. To design different electronic circuits.

### **Course Contents Summary**

| SI.<br>No. | Course Content                                                                                                                                                                                                                                                                                                                                      | Hrs. | CLOs |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| 1          | Operational amplifiers (Op-Amp): Properties of ideal Op-Amps,<br>non-inverting and inverting amplifiers, inverting integrators,<br>differentiator, weighted summer, and other applications of Op-<br>Amp circuits, effects of finite open loop gain and bandwidth on<br>circuit performance, logic signal operation of Op-Amp, dc<br>imperfections. |      | CLO1 |

| 2          | Frequency response of amplifiers: Poles, zeros and Bode plots,<br>amplifier transfer function, techniques of determining 3 dB<br>frequencies of amplifier circuits, frequency response of single-<br>stage and cascade amplifiers, frequency response of differential<br>amplifiers.                                                                |      | CLO2 |

| 3          | General purpose Op-Amp: DC analysis, small-signal analysis of<br>different stages, gain and frequency response of 741 Op-Amp.<br>Positive & Negative feedback: properties, basic topologies, and<br>feedback amplifiers with different topologies, stability, and<br>frequency compensation.                                                        |      | CLO3 |

### **Course Contents Summary**

| SI. | Course Content                                                                      | Hrs. | CLOs |

|-----|-------------------------------------------------------------------------------------|------|------|

| No. |                                                                                     |      |      |

| 4   | Active filters: Different types of filters and specifications, transfer             | 9    | CLO4 |

|     | functions, realization of first and second order low, high and                      |      |      |

|     | bandpass filters using Op-Amps.                                                     |      |      |

| 5   | Signal generators: Basic principle of sinusoidal oscillation, Op-Amp                | 6    | CLO5 |

|     | RC oscillators, LC, and crystal oscillators, Hartly oscillators, colpitt            |      |      |

|     | oscillator's clapp oscillators.                                                     |      |      |

|     | Power Amplifiers: Classification of output stages, class A, B and AB output stages. |      |      |

| Week | Content of Course                                                                                  | Teaching-<br>Learning Strategy                      | Assessment<br>Strategy         | Corresponding<br>CLOs |

|------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------|-----------------------|

| 1    | Introduction to FET:<br>Construction, operation, and<br>characteristics of JFET.                   | Lecture, Visual<br>Demonstration                    | Quiz, Problem Solving          | CLO-1                 |

| 2    | Transfer Characteristics of FET:<br>Analysis and practical examples.                               | Lecture, Practical<br>Examples, Problem<br>Solving  | Problem Solving                | CLO-1                 |

| 3    | MOSFET: Depletion and<br>enhancement types,<br>characteristics, and biasing<br>techniques.         | Lecture, Group<br>Problem Solving,<br>Demonstration | Assignment, Problem<br>Solving | CLO-2                 |

| 4    | MOSFET Amplifier Design:<br>Small signal model, analysis,<br>and biasing for MOSFET<br>amplifiers. | Lecture, Circuit<br>Simulation                      | Quiz, Written Exam             | CLO-2                 |

| Week | Course Content                                                                                    | Teaching-<br>Learning Strategy                     | Assessment<br>Strategy         | Corresponding<br>CLOs |

|------|---------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------|-----------------------|

| 5    | CMOS and VMOS Devices:<br>Characteristics, design<br>considerations, and VVR<br>applications.     | Lecture, Design<br>Activities                      | Problem Solving,<br>Assignment | CLO-2                 |

| 6    | FET Small Signal Model:<br>Equivalent circuits, voltage gain,<br>and frequency response analysis. | Lecture, Practical<br>Demonstration                | Assignment                     | CLO-2                 |

| 7    | Class Test-1                                                                                      | Review, Problem<br>Solving                         | Class Test                     | CLO-1, CLO-2          |

| 8    | Power Amplifiers: Introduction,<br>Untuned Class A and AB<br>amplifiers.                          | Lecture, Case Studies                              | Problem Solving                | CLO-3,4               |

| 9    | Power Amplifiers: Class B and<br>Class C amplifiers, push-pull<br>configurations.                 | Lecture, Practical<br>Examples, Design<br>Analysis | Quiz, Problem<br>Solving       | CLO-4,5               |

| Week | Course Content                                                                            | Teaching-<br>Learning Strategy            | Assessment<br>Strategy           | Corresponding<br>CLOs |

|------|-------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------|-----------------------|

| 10   | Tuned Power Amplifiers: Single<br>and double-tuned cascaded<br>amplifiers.                | Lecture, Circuit<br>Simulations           | Problem Solving,<br>Assignment   | CLO-3                 |

| 11   | Neutralization Techniques:<br>Applications of feedback to<br>improve amplifier stability. | Lecture, Case Studies,<br>Problem Solving | Problem Solving,<br>Written Exam | CLO-3,5               |

| 12   | Class Test-2                                                                              | Review, Problem<br>Solving                | Class Test                       | CLO-2, CLO-3,4        |

| 13   | Operational Amplifiers (P-AMP):<br>Types, characteristics, and<br>configurations.         | Lecture, Group<br>Activities              | Quiz, Problem<br>Solving         | CLO-4,5               |

| 14   | Op-Amp Applications:<br>Differentiators, integrators, and<br>comparator circuits.         | Lecture, Design<br>Activities             | Assignment, Problem<br>Solving   | CLO-4,5               |

| Week | Course Content                                                                                          | Teaching-<br>Learning Strategy       | Assessment<br>Strategy | Corresponding<br>CLOs                   |

|------|---------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------|-----------------------------------------|

| 15   | Analog Computers: Applications<br>in solving differential equations<br>using active filters.            | Lecture, Simulation,<br>Design Tasks | Written Exam           | CLO-5                                   |

| 16   | Active Filters: Low-pass, high-<br>pass, and band-pass filter design<br>using Op-Amps.                  | Lecture, Practical<br>Examples       | Problem Solving        | CLO-4,5                                 |

| 17   | Viva and Presentation:<br>Comprehensive evaluation on<br>FET, MOSFET, Power<br>Amplifiers, and Op-Amps. | Viva-Voce, Student<br>Presentations  | Viva, Presentation     | CLO-1, CLO-2,<br>CLO-3, CLO-4,<br>CLO-5 |

#### Reference Books

- \* Electronic Devices and Circuit Theory by R. Boylestad

- Other Electronics Book

#### Learning Outcome:

Student will learn about the basic theory of FET, OP-AMP, and power amplifier. They will be able to design different electronic circuits based on FET, OP-AMP, and power amplifier

#### > Teaching Methodology/Strategy

1. Power point presentation, 2. White board 3. Question-answer in the class, 4. Student's presentation, 5. Assignment

## Week - 1

### FETs vs. BJTs

#### FET>>Field Effect Transistor BJT>>Bipolar Junction Transistor Similarities:

- Amplifiers

- Switching devices

- Impedance matching circuits

#### **Few Differences:**

- FETs are voltage-controlled devices. BJTs are current controlled devices.

- FETs have a higher input impedance. BJTs have higher gains.

- FETs are less sensitive to temperature variations and are more easily integrated on ICs.

- FETs are generally more static sensitive than BJTs.

•JFET: Junction FET

•MOSFET: Metal–Oxide–Semiconductor FET

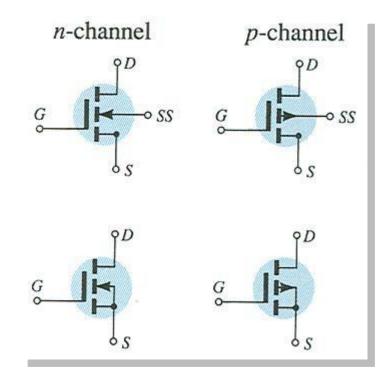

**D-MOSFET:** Depletion MOSFET**E-MOSFET:** Enhancement MOSFET

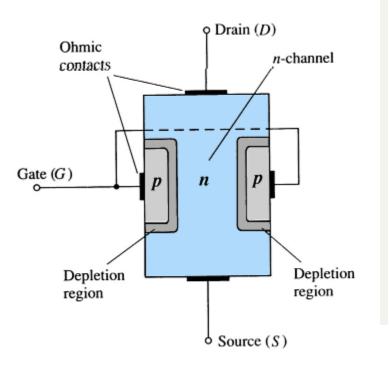

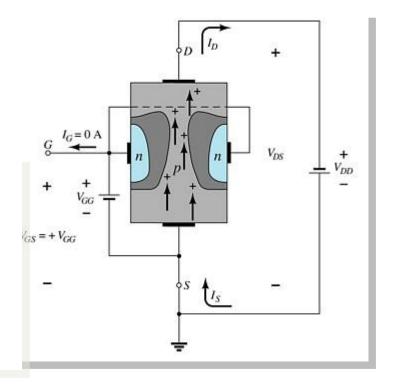

### JFET Construction

#### There are two types of JFETs

•*n*-channel •*p*-channel

The n-channel is more widely used.

There are three terminals:

Drain (D) and Source (S) are connected to the *n*-channel

Gate (G) is connected to the *p*-type material

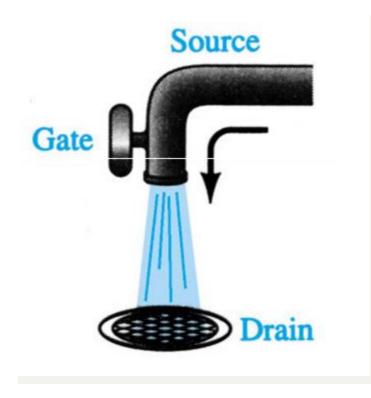

### JFET Operation: The Basic Idea

JFET operation can be compared to a water spigot.

**The source** of water pressure is the accumulation of electrons at the negative pole of the drain-source voltage.

The drain of water is the electron deficiency (or holes) at the positive pole of the applied voltage.

**The control** of flow of water is the gate voltage that controls the width of the n-channel and, therefore, the flow of charges from source to drain.

### JFET Operating Characteristics

There are three basic operating conditions for a JFET:

- $V_{GS} = 0$ ,  $V_{DS}$  increasing to some positive value

- $V_{GS} < 0$ ,  $V_{DS}$  at some positive value

- Voltage-controlled resistor

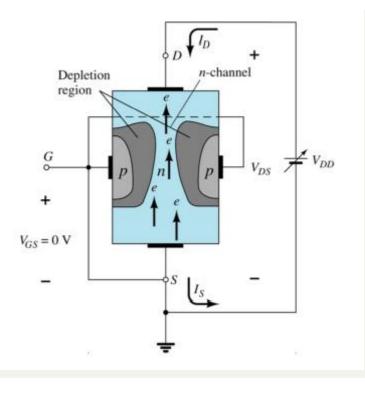

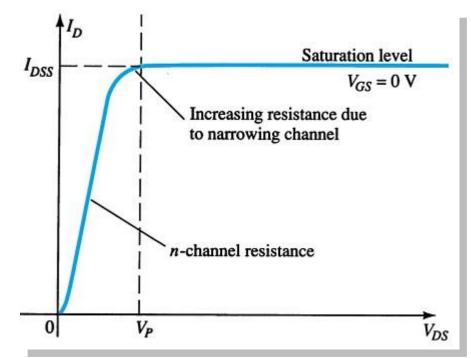

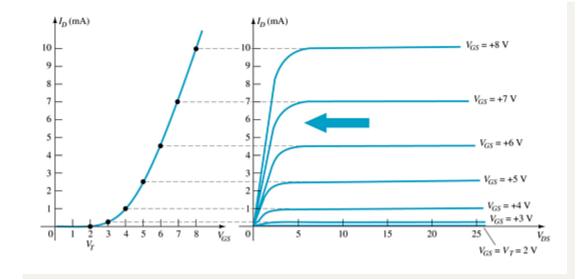

### JFET Operating Characteristics: Characteristics: $v_{GS} = 0 V/$

Three things happen when  $\mathbf{V}_{GS}$  = 0 and  $\mathbf{V}_{DS}$  is increased from 0 to a more positive voltage

- The depletion region between p-gate and n-channel increases as electrons from n-channel combine with holes from p-gate.

- Increasing the depletion region, decreases the size of the n-channel which increases the resistance of the n-channel.

- Even though the n-channel resistance is increasing, the current  $(I_D)$  from source to drain through the nchannel is increasing. This is because  $V_{DS}$  is increasing.

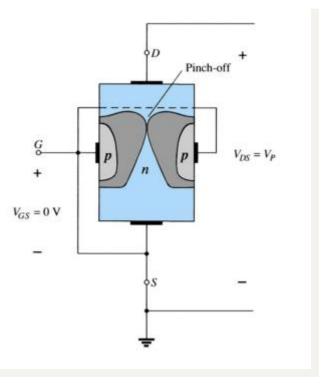

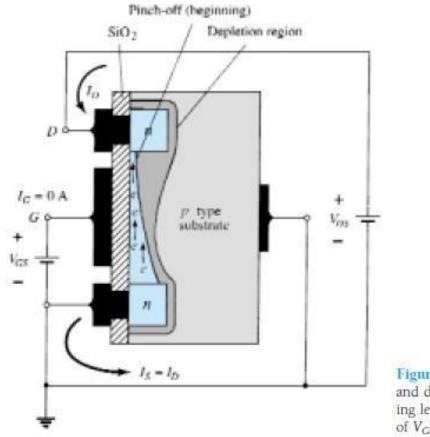

If  $V_{GS} = 0$  and  $V_{DS}$  is further increased to a more positive voltage, then the depletion zone gets so large that it **pinches off** the n-channel.

This suggests that the current in the nchannel ( $I_D$ ) would drop to 0A, but it does just the opposite-as  $V_{DS}$  increases, so does  $I_D$ .

### JFET Operating Characteristics: Saturation

At the pinch-off point:

- Any further increase in  $V_{GS}$  does not produce any increase in  $I_D$ .  $V_{GS}$  at pinch-off is denoted as  $V_p$ .

- $I_D$  is at saturation or maximum. It is referred to as  $I_{DSS}$ .

- The ohmic value of the channel is maximum.

## Week - 2

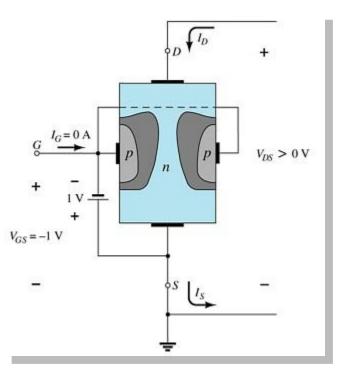

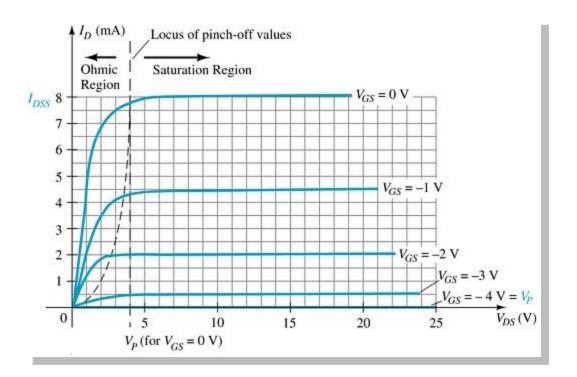

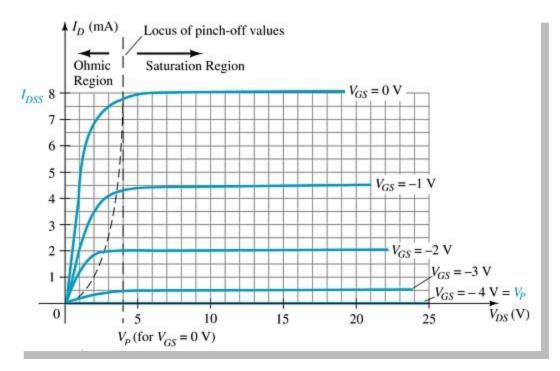

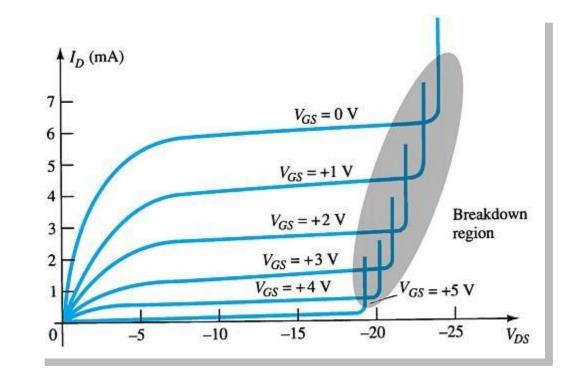

### JFET Operating Characteristics

As  $V_{GS}$  becomes more negative, the depletion region increases.

### JFET Operating Characteristics

As V<sub>GS</sub> becomes more negative:

- The JFET experiences pinch-off at a lower voltage (V<sub>P</sub>).

- $I_D$  decreases ( $I_D < I_{DSS}$ ) even though  $V_{DS}$  is increased.

- Eventually  $I_D$  reaches 0 A.  $V_{GS}$  at this point is called  $V_p$ or  $V_{GS(off)}$ ..

Also note that at high levels of  $V_{DS}$  the JFET reaches a breakdown situation.  $I_D$  increases uncontrollably if  $V_{DS} > V_{DSmax}$ .

# JFET Operating Characteristics: Voltage-Controlled Resistor

The region to the left of the pinch-off point is called the **ohmic region.**

The JFET can be used as a variable resistor, where  $V_{GS}$  controls the drain-source resistance  $(r_d)$ . As  $V_{GS}$  becomes more negative, the resistance  $(r_d)$  increases.

$$\mathbf{r_d} = \frac{\mathbf{r_o}}{\left(1 - \frac{\mathbf{V_{GS}}}{\mathbf{V_P}}\right)^2}$$

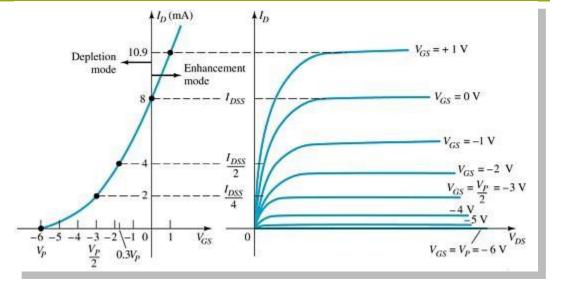

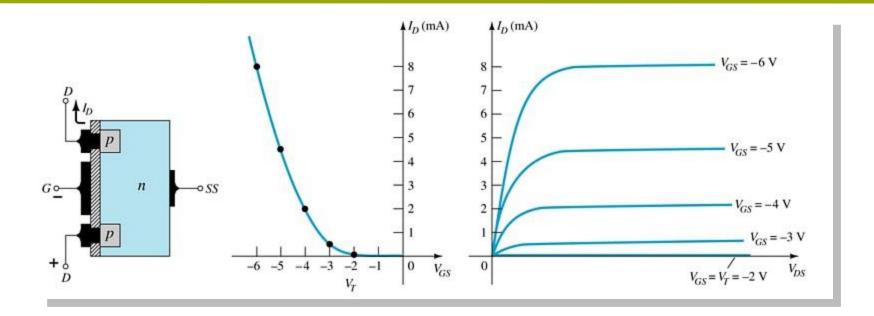

### p-Channel JFETSTS

The *p*-channel JFET behaves the same as the *n*-channel JFET, except the voltage polarities and current directions are reversed.

### p-Channel JFET Characteristics tics

As  $V_{GS}$  increases more positively

- The depletion zone increases

- $I_D$  decreases ( $I_D < I_{DSS}$ )

- Eventually  $I_D = 0 A$

Also note that at high levels of  $V_{DS}$  the JFET reaches a breakdown situation:  $I_D$  increases uncontrollably if  $V_{DS} > V_{DSmax}$ .

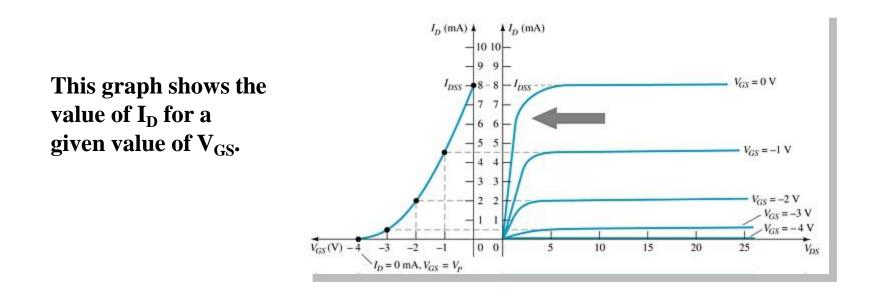

### JFET Transfer Characteristics is

The transfer characteristic of input-to-output is not as straightforward in a JFET as it is in a BJT.

In a BJT,  $\beta$  indicates the relationship between I<sub>B</sub> (input) and I<sub>C</sub> (output).

In a JFET, the relationship of  $V_{GS}$  (input) and  $I_{D}$  (output) is a little more complicated:

$$\mathbf{I_D} = \mathbf{I_{DSS}} \left( 1 - \frac{\mathbf{V_{GS}}}{\mathbf{V_P}} \right)^2 \qquad \text{Shockley's Equation}$$

### JFET Transfer Curverve

### Plotting the JFET Transfer Curverine

Using  $I_{DSS}$  and Vp ( $V_{GS(off)}$ ) values found in a specification sheet, the transfer curve can be plotted according to these three steps:

Step 1

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$$

Solving for  $V_{GS} = 0V$   $I_D = I_{DSS}$

Step 2

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right)^{2}$$

Solving for  $V_{GS} = V_{p} (V_{GS(off)})$   $I_{D} = 0A$

Step 3

Solving for

$$V_{GS} = 0V$$

to  $V_p$   $I_D = I_{DSS} \left(1 - \frac{V_{GS}}{V_P}\right)^2$

## Week - 3

**MOSFETs** have characteristics similar to JFETs and additional characteristics that make then very useful.

There are two types of MOSFETs:

- Depletion-Type

- Enhancement-Type

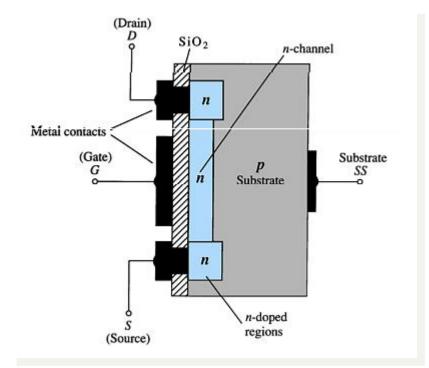

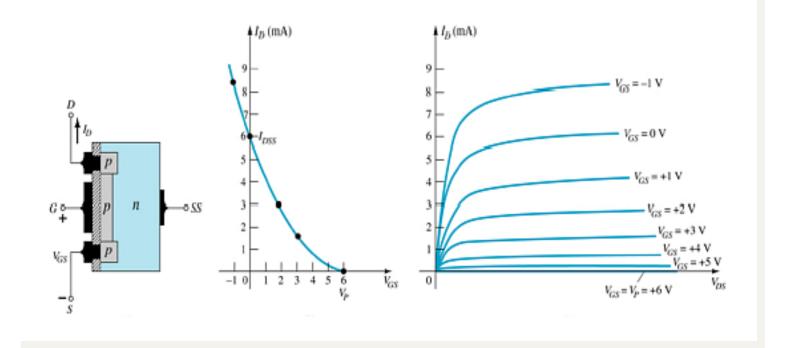

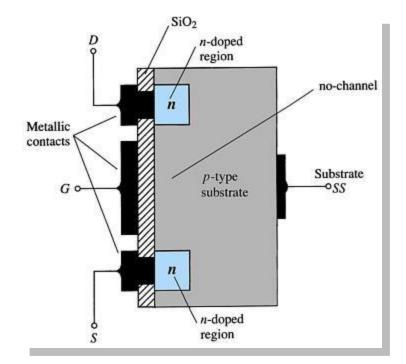

### Depletion-Type MOSFET Construction

The **Drain** (D) and **Source** (S) connect to the to *n*-doped regions. These *n*doped regions are connected via an *n*channel. This *n*-channel is connected to the **Gate** (G) via a thin insulating layer of SiO<sub>2</sub>.

The *n*-doped material lies on a *p*-doped substrate that may have an additional terminal connection called **Substrate** (SS).

### **Basic Operation and Characteristics**

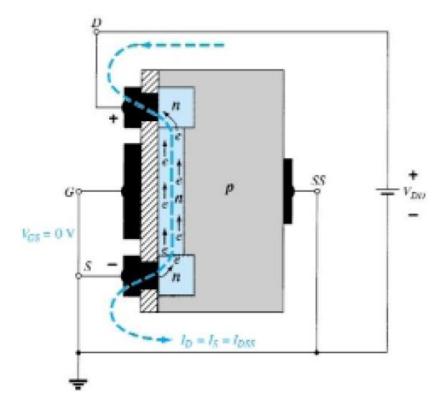

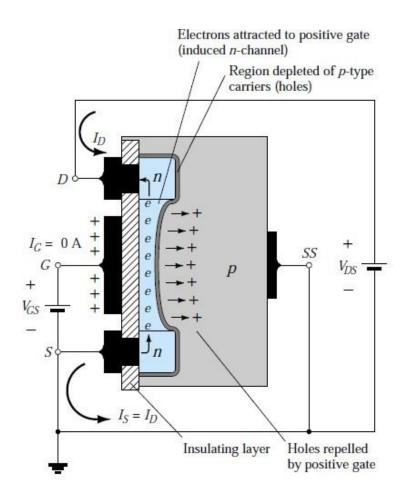

**Figure 5.24** *n*-Channel depletion-type MOSFET with  $V_{GS} = 0$  V and an applied voltage  $V_{DD}$ .

#### **Basic Operation and Characteristics**

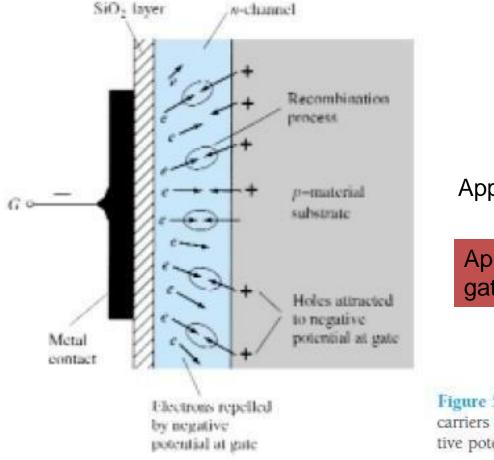

Applying negative voltage at gate

Applying positive voltage at gate?? What will happen

Figure 5.26 Reduction in free carriers in channel due to a negative potential at the gate terminal.

### **Basic MOSFET Operation**

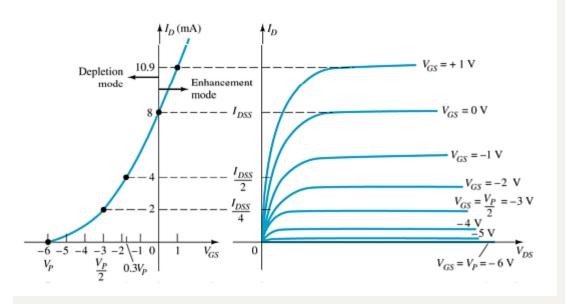

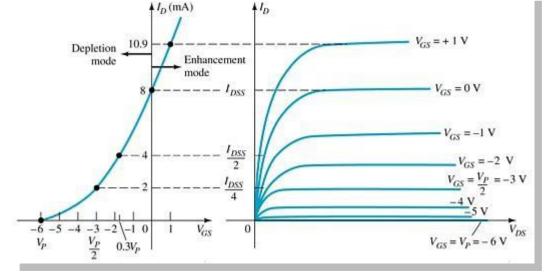

A depletion-type MOSFET can operate in two modes:

- Depletion mode

- Enhancement mode

# D-Type MOSFET in Depletion Mode de

**Depletion Mode**

The characteristics are similar to a JFET.

- When  $V_{GS} = 0$  V,  $I_D = I_{DSS}$

- When  $V_{GS} < 0 V$ ,  $I_D < I_{DSS}$

- The formula used to plot the transfer curve still applies:

$$\mathbf{I}_{\mathbf{D}} = \mathbf{I}_{\mathbf{DSS}} \left( 1 - \frac{\mathbf{V}_{\mathbf{GS}}}{\mathbf{V}_{\mathbf{P}}} \right)^2$$

# D-Type MOSFET in Enhancement Mode de

**Enhancement Mode**

- $V_{GS} > 0 V$

- I<sub>D</sub> increases above I<sub>DSS</sub>

- The formula used to plot the transfer curve still applies:

$$\mathbf{I}_{\mathbf{D}} = \mathbf{I}_{\mathbf{DSS}} \left( 1 - \frac{\mathbf{V}_{\mathbf{GS}}}{\mathbf{V}_{\mathbf{P}}} \right)^2$$

Note that  $V_{GS}$  is now a positive polarity

# p-Channel D-Type MOSFET

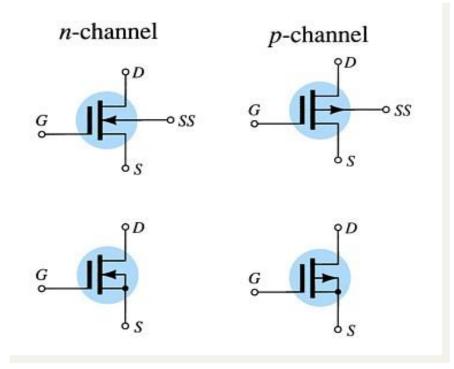

# **D-Type MOSFET Symbols**

# Week - 4

### E-Type MOSFET Construction

- The Drain (D) and Source (S) connect to the to *n*-doped regions. These *n*doped regions are connected via an *n*channel

- The Gate (G) connects to the *p*-doped substrate via a thin insulating layer of SiO<sub>2</sub>

- There is no channel

- The *n*-doped material lies on a *p*-doped substrate that may have an additional terminal connection called the **Substrate** (SS)

### **Channel Formation**

**Figure 5.32** Channel formation in the *n*-channel enhancement-type MOSFET.

Figure 5.33 Change in channel and depletion region with increasing level of  $V_{DS}$  for a fixed value of  $V_{GS}$ .

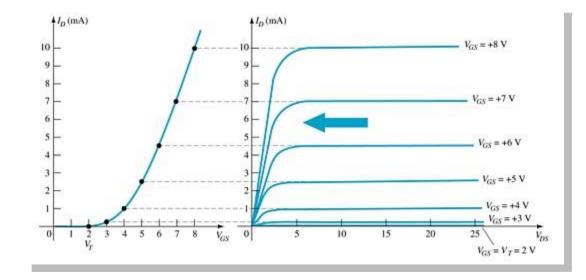

### Basic Operation of the E-Type MOSFET

### The enhancement-type MOSFET operates only in the enhancement mode.

- $V_{GS}$  is always positive

- As V<sub>GS</sub> increases, I<sub>D</sub> increases

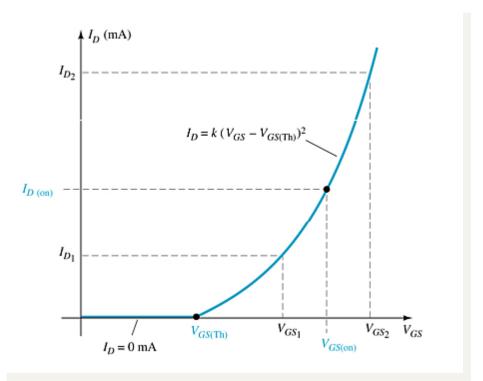

## E-Type MOSFET Transfer Curve urve

To determine I<sub>D</sub> given V<sub>GS</sub>:

$I_{\mathbf{D}} = \mathbf{k}(\mathbf{V}_{\mathbf{GS}} - \mathbf{V}_{\mathbf{T}})^2$

Where:

$V_T$  = threshold voltage or voltage at which the MOSFET turns on

*k*, a constant, can be determined by using values at a specific point and the formula:

$$k = \frac{I_{D(ON)}}{\binom{V_{GS}(ON) - V_{T}}{V_{T}}}$$

**V**<sub>DSsat</sub> can be calculated by:

$$\mathbf{V_{Dsat}} = \mathbf{V_{GS}} - \mathbf{V_{T}}$$

# p-Channel E-Type MOSFETs

The *p*-channel enhancement-type MOSFET is similar to the *n*channel, except that the voltage polarities and current directions are reversed.

### **MOSFET Symbols**

# Handling MOSFETs Ts

MOSFETs are very sensitive to static electricity. Because of the very thin SiO<sub>2</sub> layer between the external terminals and the layers of the device, any small electrical discharge can create an unwanted conduction.

### Protection

- Always transport in a static sensitive bag

- Always wear a static strap when handling MOSFETS

- •

- Apply voltage limiting devices between the gate and source, such as back-to-back Zeners to limit any transient voltage.

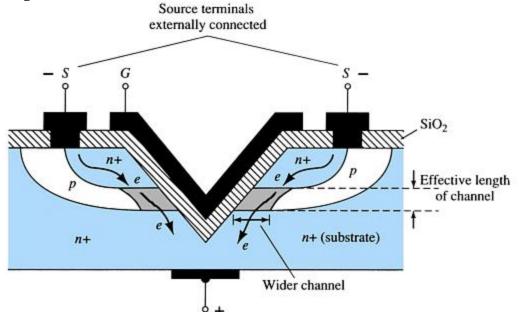

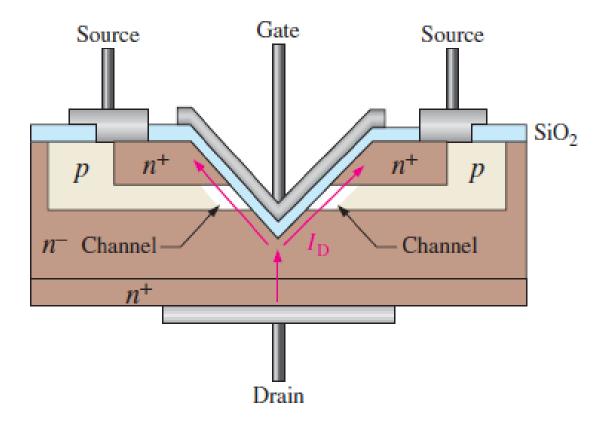

### VMOS Devices

### VMOS (vertical MOSFET) increases the surface area of the device.

#### Advantages

- VMOS devices handle higher currents by providing more surface area to dissipate the heat.

- VMOS devices also have faster switching times.

- VMOS FETs have a positive temperature coefficient that will combat the possibility of thermal runaway

One of the disadvantages of the typical MOSFET is the reduced power-handling levels (typically, less than 1 W) compared to BJT transistors.

decreasing channel lengths result in reduced resistance levels, the power dissipation level of the device (power lost in the form of heat) at operating current levels will be reduced. In addition, the contact area between the channel and the *n* region is greatly increased by the vertical mode construction, contributing to a further decrease in the resistance level and an increased area for current between the doping layers

n<sup>+</sup> substrate where n<sup>+</sup> means a higher doping level than n<sup>-</sup>

# Week - 5

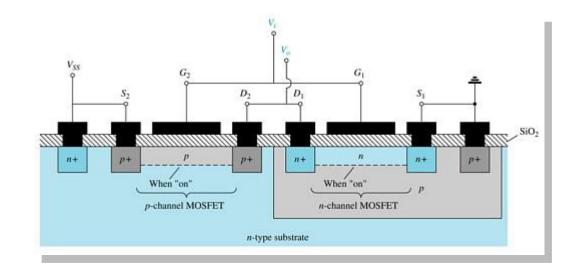

### CMOS Devices

CMOS (complementary MOSFET) uses a *p*-channel and *n*-channel MOSFET; often on the same substrate as shown here.

#### Advantages

- Useful in logic circuit designs

- Higher input impedance

- Faster switching speeds

- Lower operating power levels

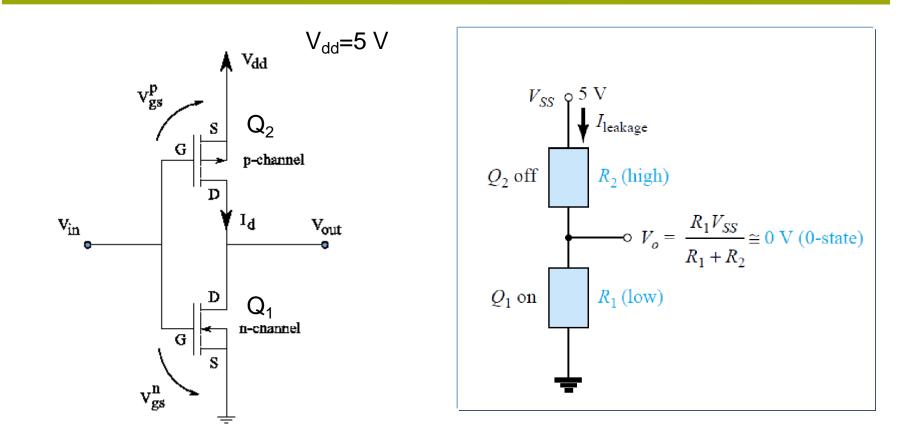

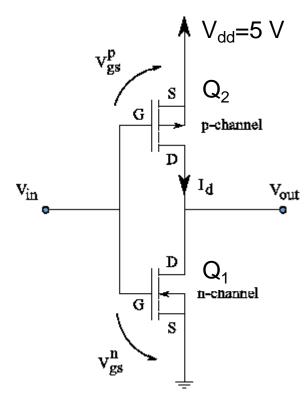

#### **CMOC** Inverter

### CMOC Inverter: Operation

| V | in | V <sub>gs(n)</sub> | V <sub>gs(p)</sub> | <b>Q</b> <sub>1</sub> | Q <sub>2</sub> | V <sub>out</sub> |

|---|----|--------------------|--------------------|-----------------------|----------------|------------------|

| 5 | V  | +5                 | 0                  | On/short              | Off/open       | 0                |

| 0 | V  | 0                  | -5                 | Off/open              | On/short       | 5                |

|   |    |                    |                    |                       |                |                  |

|   |    |                    |                    |                       |                |                  |

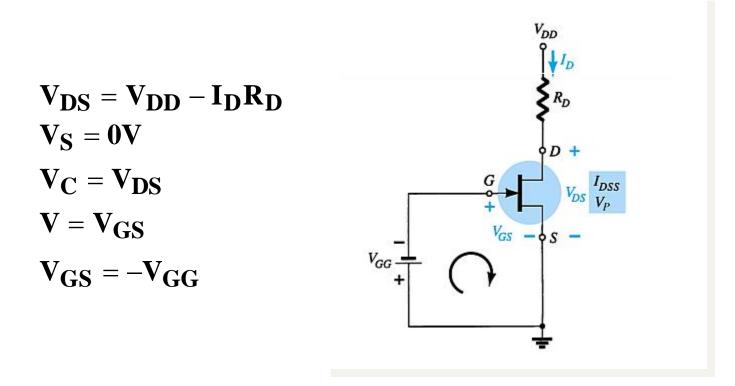

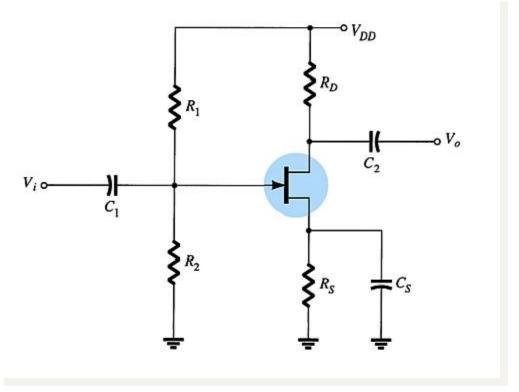

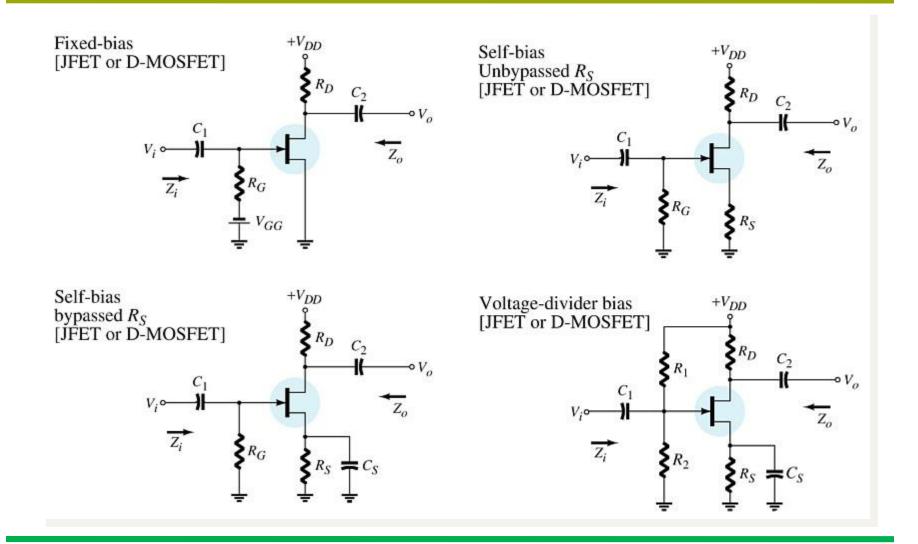

### **Common FET Biasing Circuits**

**JFET Biasing Circuits**

- Fixed Bias

- Self-Bias

- Voltage-Divider Bias

**D-Type MOSFET Biasing Circuits**

•Self-Bias

•Voltage-Divider Bias

**E-Type MOSFET Biasing Circuits**

Feedback ConfigurationVoltage-Divider Bias

Basic Current Relationships

#### For all FETs:

$$I_G \cong 0A$$

$I_D = I_S$

#### **For JFETS and D-Type MOSFETs:**

$$\mathbf{I}_{\mathbf{D}} = \mathbf{I}_{\mathbf{DS}\,\mathbf{S}} \left(1 - \frac{\mathbf{V}_{\mathbf{GS}}}{\mathbf{V}_{\mathbf{P}}}\right)^2$$

**For E-Type MOSFETs:**

$$\mathbf{I}_{\mathbf{D}} = \mathbf{k}(\mathbf{V}_{\mathbf{GS}} - \mathbf{V}_{\mathbf{T}})^2$$

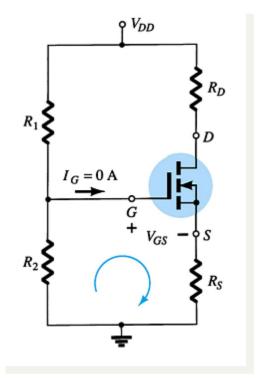

### **Self-Bias Configuration**

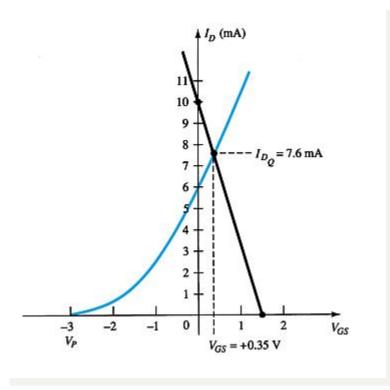

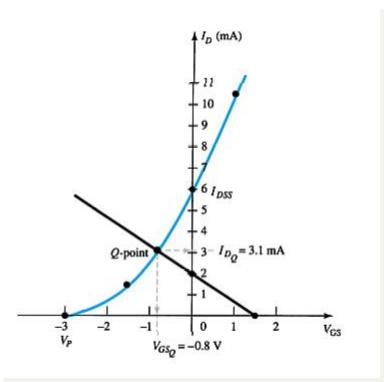

For the indicated loop,  $V_{GS} = -I_DR_S$ To solve this equation:

- Select an  $I_D < I_{DSS}$  and use the component value of  $R_S$  to calculate  $V_{GS}$

- Plot the point identified by  $I_D$  and  $V_{GS}$ . Draw a line from the origin of the axis to this point.

- Plot the transfer curve using  $I_{DSS}$  and  $V_P (V_P = V_{GSoff} \text{ in specification sheets})$  and a few points such as  $I_D = I_{DSS}/4$  and  $I_D = I_{DSS}/2$  etc.

The Q-point is located where the first line intersects the transfer curve. Use the value of  $I_D$  at the Q-point  $(I_{DQ})$  to solve for the other voltages:

$$\begin{split} \mathbf{V_{DS}} &= \mathbf{V_{DD}} - \mathbf{I_D}(\mathbf{R_S} + \mathbf{R_D}) \\ \mathbf{V_S} &= \mathbf{I_D}\mathbf{R_S} \\ \mathbf{V_D} &= \mathbf{V_{DS}} + \mathbf{V_S} = \mathbf{V_{DD}} - \mathbf{V_{RD}} \end{split}$$

$I_G = 0 A$

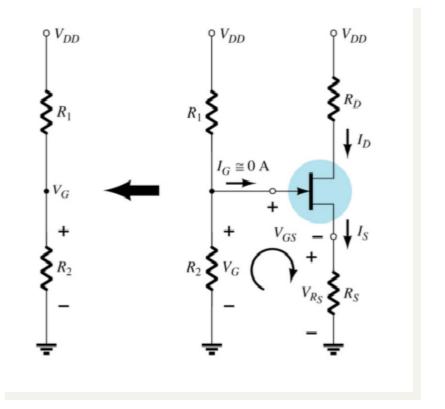

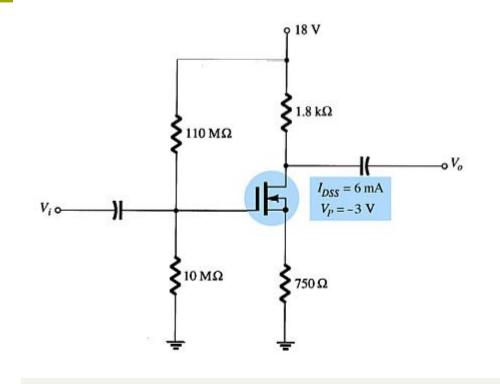

V<sub>G</sub> is equal to the voltage across divider resistor R<sub>2</sub>:

$$\mathbf{V}_G = \frac{\mathbf{R}_2 \mathbf{V}_{DD}}{\mathbf{R}_1 + \mathbf{R}_2}$$

**Using Kirchhoff's Law:**

$$\mathbf{V}_{\mathbf{GS}} = \mathbf{V}_{\mathbf{G}} - \mathbf{I}_{\mathbf{D}}\mathbf{R}_{\mathbf{S}}$$

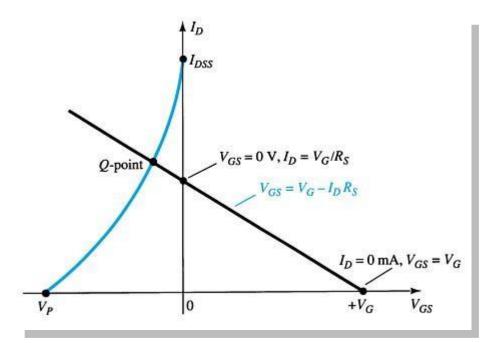

The Q point is established by plotting a line that intersects the transfer curve.

Week - 6

### Voltage-Divider Q-point

### Step 1

### Plot the line by plotting two points: $\cdot V_{GS} = V_G$ , $I_D = 0 A$ $\cdot V_{GS} = 0 V$ , $I_D = V_G / R_S$

#### Step 2

Plot the transfer curve by plotting  $I_{DSS}$ ,  $V_P$  and the calculated values of  $I_D$

#### Step 3

The Q-point is located where the line intersects the transfer curve

### **Voltage-Divider Bias Calculations**

Using the value of  $I_D$  at the Q-point, solve for the other variables in the voltagedivider bias circuit:

$$V_{DS} = V_{DD} - I_D (R_D + R_S)$$

$$V_D = V_{DD} - I_D R_D$$

$$V_S = I_D R_S$$

$$I_{R1} = I_{R2} = \frac{V_{DD}}{R_1 + R_2}$$

Depletion-type MOSFET bias circuits are similar to those used to bias JFETs. The only difference is that depletion-type MOSFETs can operate with positive values of  $V_{GS}$  and with  $I_D$  values that exceed  $I_{DSS}$ .

#### Step 1

#### **Plot line for**

$$\bullet \mathbf{V}_{GS} = \mathbf{V}_{G}, \mathbf{I}_{D} = \mathbf{0} \mathbf{A}$$

$$\bullet \mathbf{I}_{D} = \mathbf{V}_{G}/\mathbf{R}_{S}, \mathbf{V}_{GS} = \mathbf{0} \mathbf{V}$$

#### Step 2

Plot the transfer curve using  $I_{DSS}, V_{P}$  and calculated values of  $I_{D}$

#### Step 3

The Q-point is located where the line intersects the transfer curve. Use the  $I_D$  at the Q-point to solve for the other variables in the voltage-divider bias circuit.

These are the same steps used to analyze JFET self-bias circuits.

### Voltage-Divider Bias

#### Step 1

#### Plot the line for

#### Step 2

Plot the transfer curve using  $I_{DSS}$ ,  $V_P$  and calculated values of  $I_D$ .

#### Step 3

The Q-point is located where the line intersects the transfer curve is. Use the  $I_D$  at the Q-point to solve for the other variables in the voltage-divider bias circuit.

These are the same steps used to analyze JFET voltage-divider bias circuits.

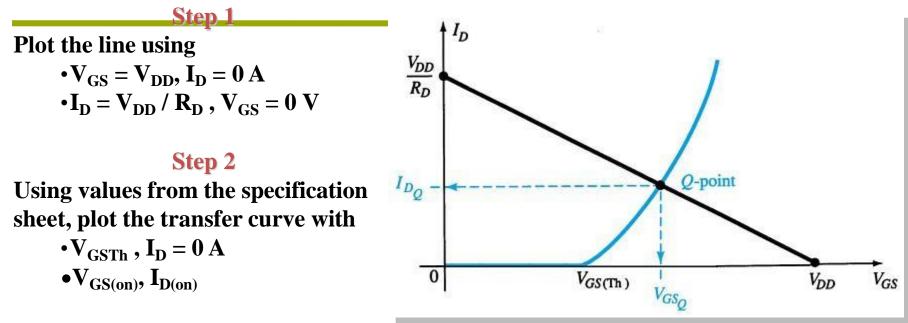

#### E-Type MOSFET Bias Circuits

The transfer characteristic for the e-type MOSFET is very different from that of a simple JFET or the d-type MOSFET.

### Feedback Bias Circuit

#### Feedback Bias Q-Point

#### Step 3

The Q-point is located where the line and the transfer curve intersect

#### Step 4

Using the value of  $I_D$  at the Q-point, solve for the other variables in the bias circuit

Plot the line and the transfer curve to find the Q-point. Use these equations:

$$\begin{split} \mathbf{V}_G &= \frac{\mathbf{R}_2 \mathbf{V}_{DD}}{\mathbf{R}_1 + \mathbf{R}_2} \\ \mathbf{V}_{GS} &= \mathbf{V}_G - \mathbf{I}_D \mathbf{R}_S \\ \mathbf{V}_{DS} &= \mathbf{V}_{DD} - \mathbf{I}_D \left(\mathbf{R}_S + \mathbf{R}_D\right) \end{split}$$

#### Step 1

**Plot the line using**

•

$$V_{GS} = V_G = (R_2 V_{DD}) / (R_1 + R_2), I_D = 0 A$$

• $I_D = V_G / R_S, V_{GS} = 0 V$

#### Step 2

Using values from the specification sheet, plot the transfer curve with

•

$$V_{GSTh}$$

,  $I_D = 0 A$

• $V_{GS(on)}$ ,  $I_{D(on)}$

#### Step 3

The point where the line and the transfer curve intersect is the **Q**-point.

#### Step 4

Using the value of  $\mathbf{I}_{\mathrm{D}}$  at the Q-point, solve for the other circuit values.

## Week - 7

Voltage-controlled resistor JFET voltmeter Timer network Fiber optic circuitry MOSFET relay driver

### > Approach 1: Graphical solution

- Draw line for V<sub>GS</sub>

- Draw transfer curve

- Find intersection

#### > Approach 2: Mathematical Solution

- Solve the two equations

- VGS

- Transfer equation

#### Introduction Introduction

#### **FETs provide:**

- Excellent voltage gain

- High input impedance

- Low-power consumption

- Good frequency range

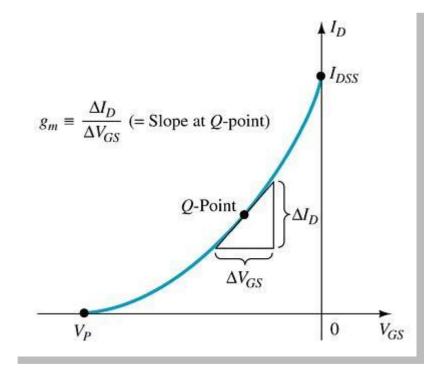

### FET Small-Signal Model FET Small-Signal Model

#### Transconductance

The relationship of a change in  $I_{\rm D}$  to the corresponding change in  $V_{\rm GS}$  is called transconductance

Transconductance is denoted  $g_m$  and given by:

$$\mathbf{g}_{\mathbf{m}} = \frac{\Delta \mathbf{I}_{\mathbf{D}}}{\Delta \mathbf{V}_{\mathbf{GS}}}$$

# **Graphical Determination of g<sub>m</sub>**

## Mathematical Definitions of gm efinitions of gm

$$g_{m} = \frac{\Delta I_{D}}{\Delta V_{GS}}$$

$$g_{m} = \frac{2I_{DSS}}{|V_{P}|} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]$$

Where  $V_{GS} = 0V$   $g_{m0} = \frac{2I_{DSS}}{|V_{P}|}$

$$g_{m} = g_{m0} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]$$

Where  $1 - \frac{V_{GS}}{V_{P}} = \sqrt{\frac{I_{D}}{I_{DSS}}}$

$$g_{m} = g_{m0} \left( 1 - \frac{V_{GS}}{V_{P}} \right) = g_{m0} \sqrt{\frac{I_{D}}{I_{DSS}}}$$

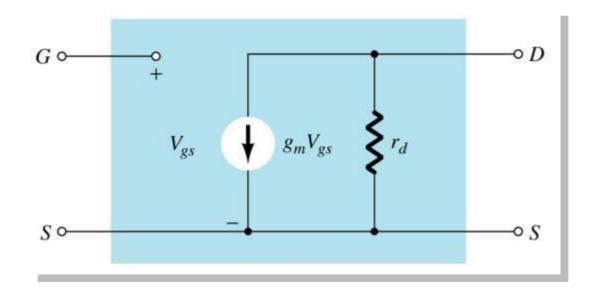

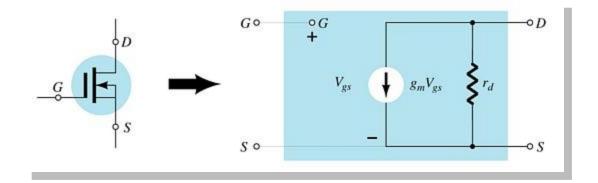

#### FET Impedance FET Impedance

**Input impedance:**

$$Z_i = \infty \Omega$$

**Output Impedance:**

$$\mathbf{Z}_{\mathbf{o}} = \mathbf{r}_{\mathbf{d}} = \frac{1}{\mathbf{y}_{\mathbf{o}\mathbf{s}}}$$

where:

$$\mathbf{r}_{\mathbf{d}} = \frac{\Delta \mathbf{V}_{\mathbf{DS}}}{\Delta \mathbf{I}_{\mathbf{D}}} \Big| \mathbf{V}_{\mathbf{GS}} = \text{constant}$$

$y_{os}$ = admittance parameter listed on FET specification sheets.

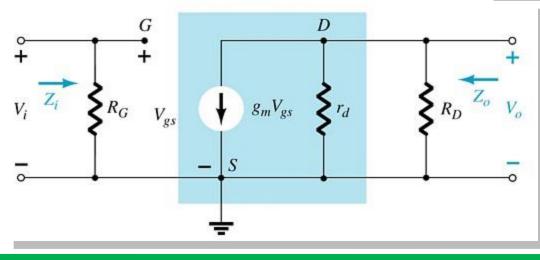

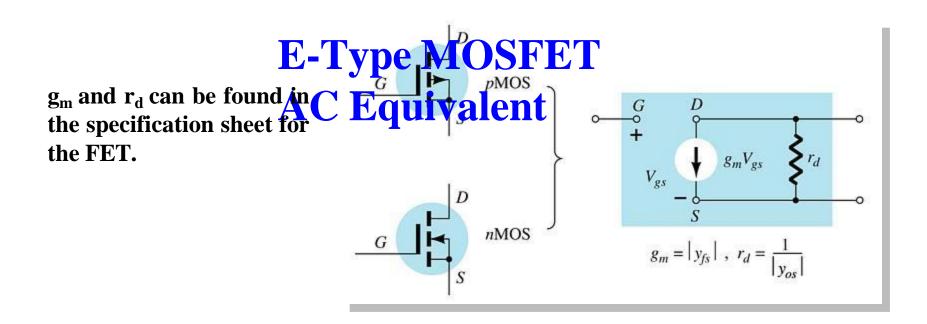

### FET AC Equivalent Circuit

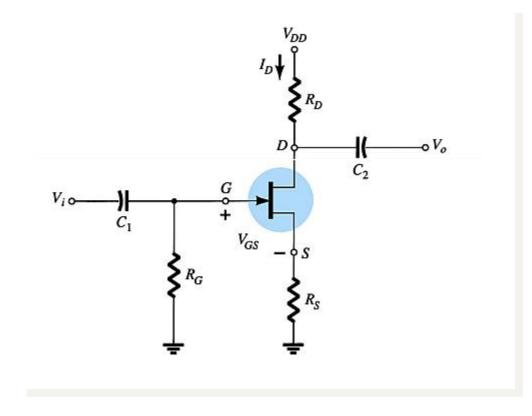

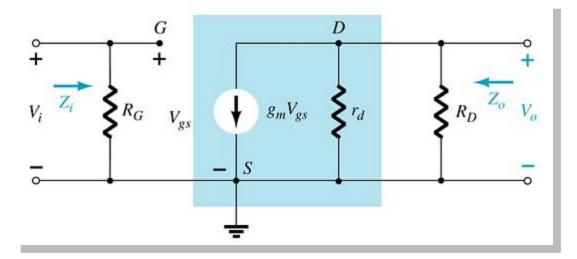

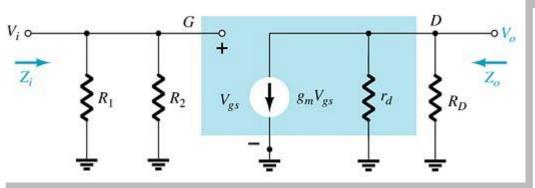

#### Common-Source (CS) Fixed-Bias Circuit Common-Source (CS) Fixed-Bias Circuit

The input is on the gate and the output is on the drain

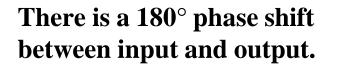

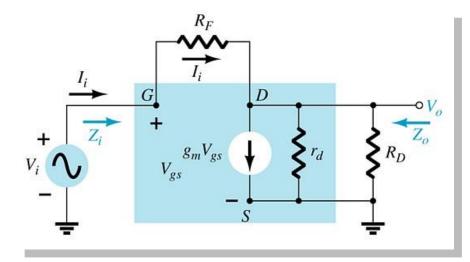

There is a 180° phase shift between input and output

Week - 8

#### Calculations Calculations

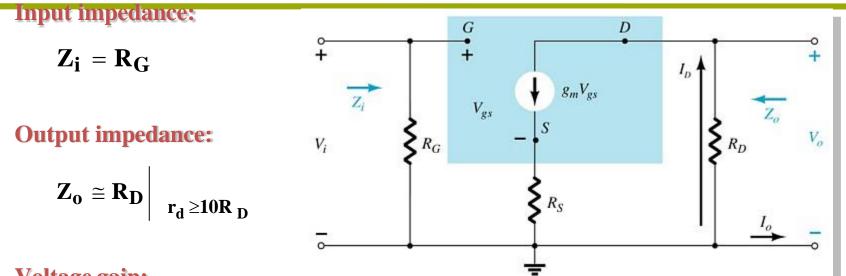

**Input impedance:**

$Z_i = R_G$

**Output impedance:**

$\begin{aligned} \mathbf{Z}_{o} &= \mathbf{R}_{D} \parallel \mathbf{r}_{d} \\ \mathbf{Z}_{o} &\cong \mathbf{R}_{D} \\ \mid \mathbf{r}_{d} \geq & 10\mathbf{R}_{D} \end{aligned}$

$$\mathbf{A}_{\mathbf{V}} = \frac{\mathbf{V}_{\mathbf{0}}}{\mathbf{V}_{\mathbf{i}}} = -\mathbf{g}_{\mathbf{m}} \left( \mathbf{r}_{\mathbf{d}} \parallel \mathbf{R}_{\mathbf{D}} \right)$$

$$\mathbf{A}_{\mathbf{V}} = \frac{\mathbf{V}_{\mathbf{0}}}{\mathbf{V}_{\mathbf{i}}} = -\mathbf{g}_{\mathbf{m}} \mathbf{R}_{\mathbf{D}} \Big|_{\mathbf{r}_{\mathbf{d}} \ge 10 \mathbf{R}_{\mathbf{D}}}$$

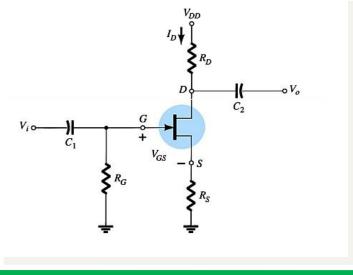

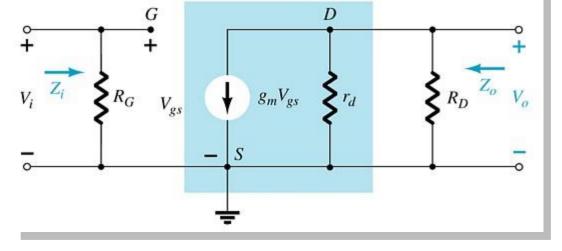

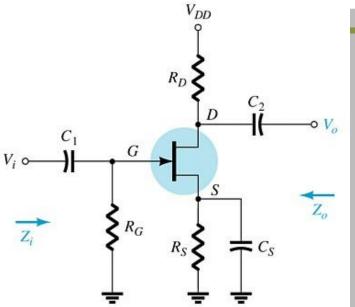

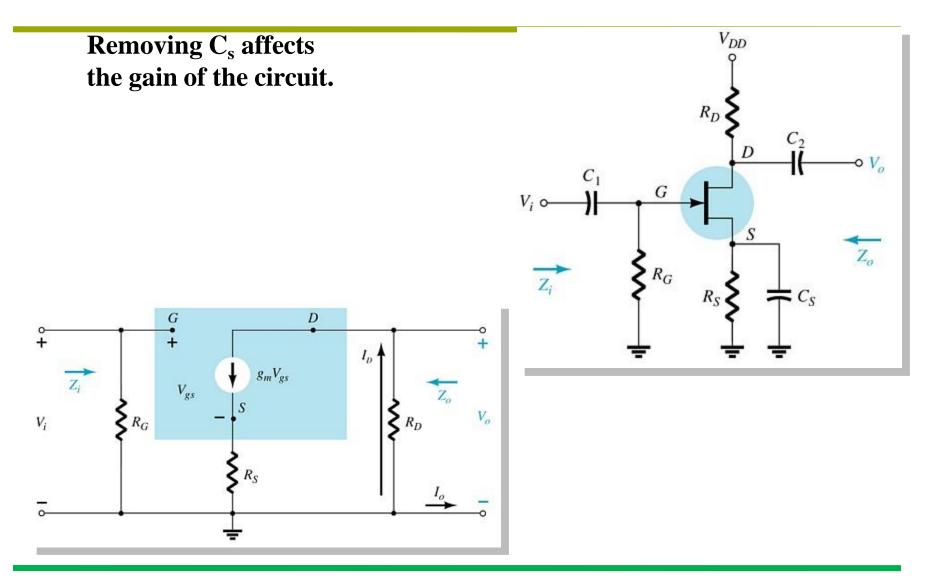

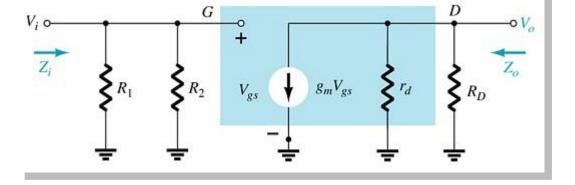

### Common-Source (CS) Self-Bias Circuit Common-Source (CS) Self-Bias Circuit

This is a common-source amplifier configuration, so the input is on the gate and the output is on the drain

There is a 180° phase shift between input and output

### Calculations

**Input impedance:**

$Z_i = R_G$

**Output impedance:**

$$\mathbf{A}_{\mathbf{v}} = -\mathbf{g}_{\mathbf{m}} (\mathbf{r}_{\mathbf{d}} \parallel \mathbf{R}_{\mathbf{D}})$$

$$\mathbf{A}_{\mathbf{v}} = -\mathbf{g}_{\mathbf{m}} \mathbf{R}_{\mathbf{D}} \Big|_{\mathbf{r}_{\mathbf{d}} \ge 10\mathbf{R}_{\mathbf{D}}}$$

### **Common-Source (CS) Self-Bias Circuit**

### Calculations

$$\begin{split} \mathbf{A}_{v} &= \frac{V_{o}}{V_{i}} = -\frac{g_{m}R_{D}}{1+g_{m}R_{S} + \frac{R_{D} + R_{S}}{r_{d}}} \\ \mathbf{A}_{v} &= \frac{V_{o}}{V_{i}} = -\frac{g_{m}R_{D}}{1+g_{m}R_{S}} \Big| \mathbf{r}_{d} \ge 10(R_{D} + R_{S}) \end{split}$$

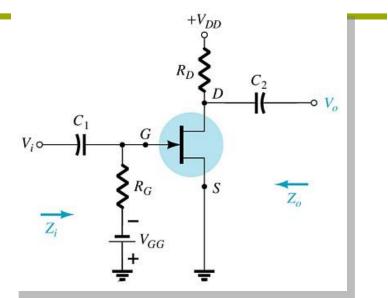

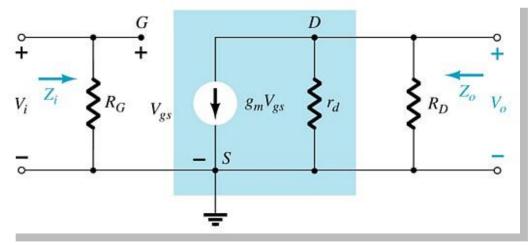

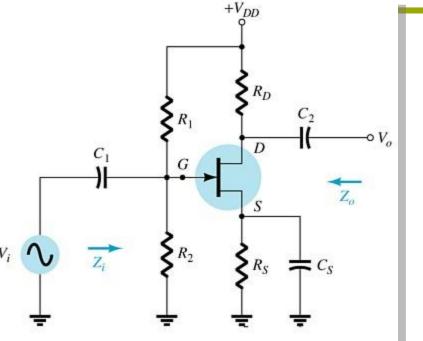

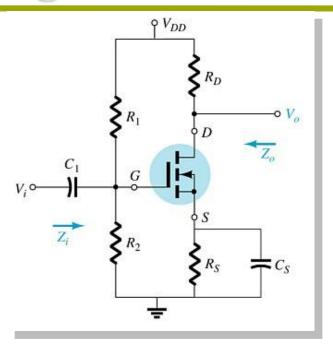

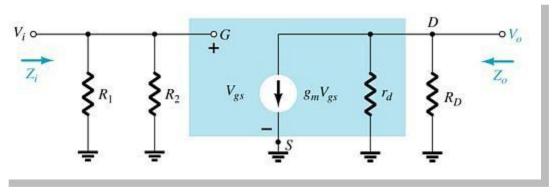

## Common-Source (CS) Voltage-Divider Bias Common-Source (CS) Voltage-Divider Bias

This is a common-source amplifier configuration, so the input is on the gate and the output is on the drain.

#### Impedances Impedances

**Input impedance:**

$Z_i=R_1 \parallel R_2$

**Output impedance:**

$$\begin{split} & \mathbf{Z}_o = \mathbf{r}_d \parallel \mathbf{R}_D \\ & \mathbf{Z}_o \, \cong \, \mathbf{R}_D \bigg|_{\substack{\mathbf{r}_d \geq 10 \mathbf{R}_D}} \end{split}$$

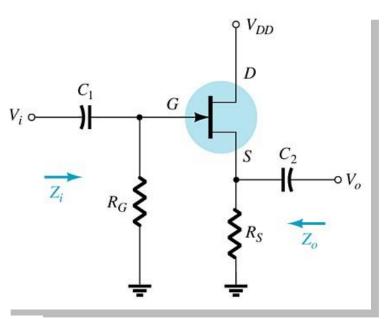

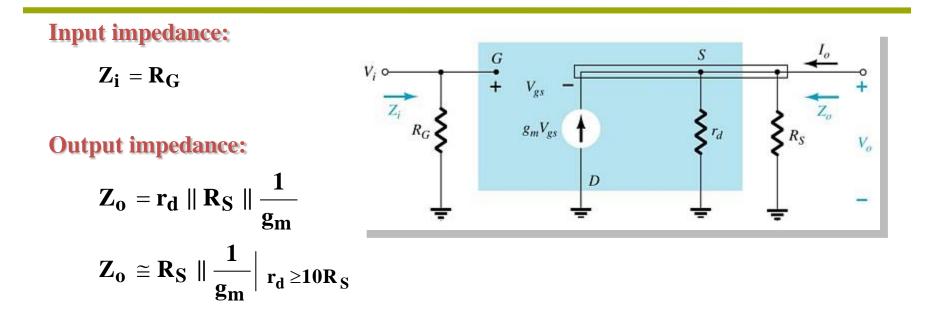

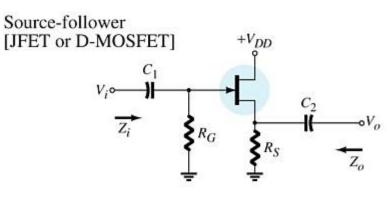

## Source Follower (Common-Drain) Circuit Source Follower (Common-Drain) Circuit

In a common-drain amplifier configuration, the input is on the gate, but the output is from the source.

There is no phase shift between input and output.

### Impedances

$$\begin{split} \mathbf{A}_{v} &= \frac{\mathbf{V}_{o}}{\mathbf{V}_{i}} = \frac{\mathbf{g}_{m} \left(\mathbf{r}_{d} \parallel \mathbf{R}_{S}\right)}{1 + \mathbf{g}_{m} \left(\mathbf{r}_{d} \parallel \mathbf{R}_{S}\right)} \\ \mathbf{A}_{v} &= \frac{\mathbf{V}_{o}}{\mathbf{V}_{i}} = \frac{\mathbf{g}_{m} \mathbf{R}_{S}}{1 + \mathbf{g}_{m} \mathbf{R}_{S}} \Big|_{\mathbf{r}_{d}} \ge 10 \end{split}$$

Week - 9

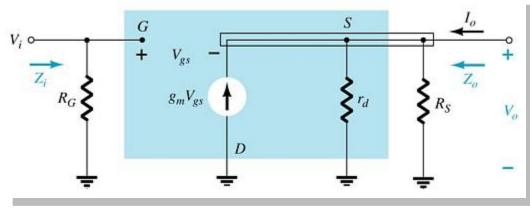

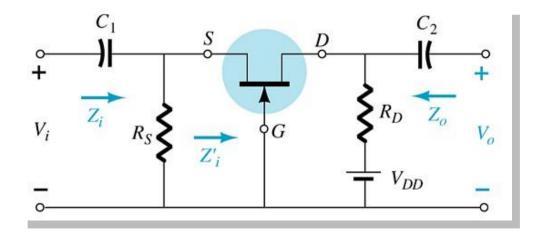

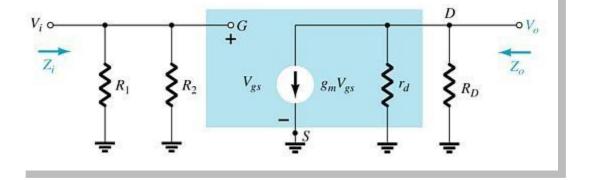

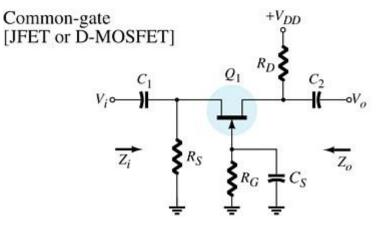

#### Common-Gate (CG) Circuit Common-Gate (CG) Circuit

The input is on the source and the output is on the drain.

There is no phase shift between input and output.

#### Calculations Calculations

**Input impedance:**

$$\begin{split} \mathbf{Z}_i &= \mathbf{R}_S ~ \| \left[ \frac{\mathbf{r}_d + \mathbf{R}_D}{1 + \mathbf{g}_m \mathbf{r}_d} \right] \\ \mathbf{Z}_i &\cong \mathbf{R}_S ~ \| \frac{1}{\mathbf{g}_m} \Big|_{\mathbf{r}_d \geq 10R_D} \end{split}$$

#### $r_d$ + $C_1$ $C_2$ D S a + $g_m V_{gs}$ $Z'_o$ Zo $Z_i$ $\sum R_D$ $V_i$ $R_S \leqslant$ $V_{gs}$ Vo +G

#### **Output impedance:**

$$\begin{aligned} \mathbf{Z}_{\mathbf{o}} &= \mathbf{R}_{\mathbf{D}} \parallel \mathbf{r}_{\mathbf{d}} \\ \mathbf{Z}_{\mathbf{o}} &\cong \mathbf{R}_{\mathbf{D}} \mid_{\mathbf{r}_{\mathbf{d}} \ge 10} \end{aligned}$$

$$\mathbf{A}_{v} = \frac{\mathbf{V}_{o}}{\mathbf{V}_{i}} = \frac{\left[ \frac{\mathbf{g}_{m} \mathbf{R}_{D} + \frac{\mathbf{R}_{D}}{\mathbf{r}_{d}} \right]}{\left[ 1 + \frac{\mathbf{R}_{D}}{\mathbf{r}_{d}} \right]} \quad \mathbf{A}_{v} = \mathbf{g}_{m} \mathbf{R}_{D} \left| \mathbf{r}_{d} \ge 10 \mathbf{R}_{D} \right|$$

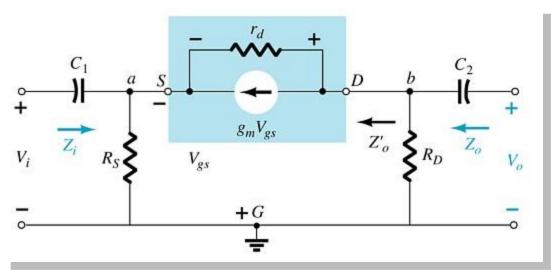

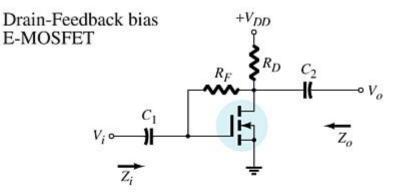

### **E-Type MOSFET AC Equivalent**

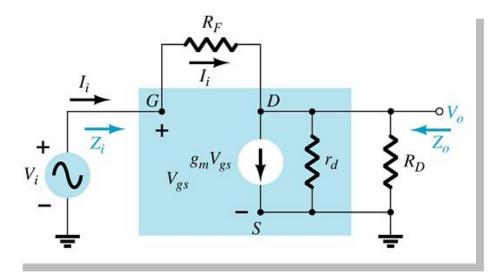

## Common-Source Drain-Feedback

#### Calculations Calculations

**Input impedance:**

$$\begin{split} \mathbf{Z}_{i} &= \frac{\mathbf{R}_{F} + \mathbf{r}_{d} \parallel \mathbf{R}_{D}}{1 + \mathbf{g}_{m} \left( \mathbf{r}_{d} \parallel \mathbf{R}_{D} \right)} \\ \mathbf{Z}_{i} &\cong \frac{\mathbf{R}_{F}}{1 + \mathbf{g}_{m} \mathbf{R}_{D}} \Big|_{\mathbf{R}_{F}} >> \mathbf{r}_{d} \parallel \mathbf{R}_{D}, \mathbf{r}_{d} \ge 10 \mathbf{R}_{D} \end{split}$$

#### **Output impedance:**

$$\begin{split} & \mathbf{Z}_o = \mathbf{R}_F ~||~ \mathbf{r}_d ~|| \mathbf{R}_D \\ & \mathbf{Z}_o ~\cong \mathbf{R}_D \Big|_{\mathbf{R}_F >> \mathbf{r}_d ~|| \mathbf{R}_D ~, \mathbf{r}_d \geq 10 \mathbf{R}_D} \end{split}$$

# Week - 10

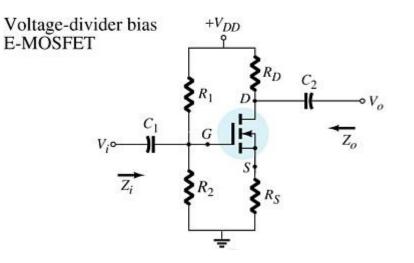

### **Common-Source Voltage-Divider Bias**

#### Calculations Calculations

**Input impedance:**

$\mathbf{Z}_i{=}R_1||\ R_2$

Output impedance:  $Z_{o} = r_{d} \parallel R_{D}$   $Z_{o} \cong R_{D} \mid_{r_{d} \ge 10}$

$$\begin{split} \mathbf{A}_{\mathbf{V}} &= -\mathbf{g}_{\mathbf{m}}(\mathbf{r}_{\mathbf{d}} \parallel \mathbf{R}_{\mathbf{D}}) \\ \mathbf{A}_{\mathbf{V}} &\cong -\mathbf{g}_{\mathbf{m}}\mathbf{R}_{\mathbf{D}} \Big|_{\mathbf{r}_{\mathbf{d}} \geq 10\mathbf{R}_{\mathbf{D}}} \end{split}$$

## Summary Table Table

#### more...

### **Summary Table**

## Troubleshooting **Troubleshooting**

Check the DC bias voltages:

Check the DC bias voltages:

**Check the AC voltages:**

If not correct check power supply, resistors, FET. Also check to ensure that the coupling capacitor between amplifier stages is OK.

Check the AC voltages:

If not correct check FET, capacitors and the loading effect of the next stage

## Week - 11

### EE 2209 Electronics-II Operational Amplifier

Basic Op-Amp

## **Basic Op-Amp**

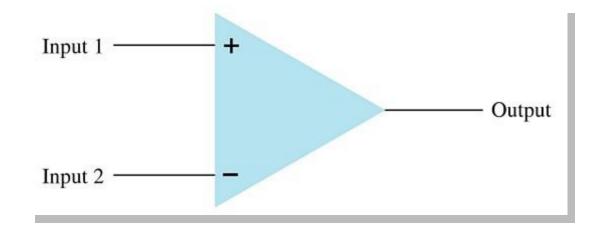

Operational amplifier or op-amp, is a very high gain differential amplifier with a high input impedance (typically a few meg-Ohms) and low output impedance (less than 100  $\Omega$ ).

Note the op-amp has two inputs and one output.

A differential amplifier is a type of electronic amplifier that amplifies the difference between two input voltages but suppresses any voltage common to the two inputs.

Op-Amp Gain

Op-Amp Gain

**Op-Amps have a very high gain. They can be connected open-loop or closed-loop.**

- **Open-loop** refers to a configuration where there is no feedback from output back to the input. In the open-loop configuration the gain can exceed **10,000**.

- Closed-loop configuration reduces the gain. In order to control the gain of an op-amp it must have feedback. This feedback is a negative feedback. A negative feedback reduces the gain and improves many characteristics of the op-amp.

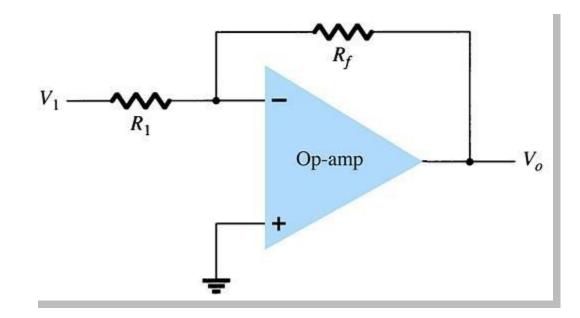

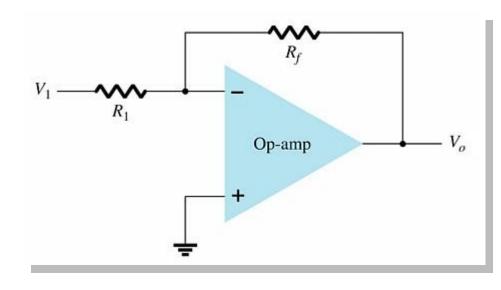

#### Inverting Op-Amp

# **Inverting Op-Amp**

- The signal input is applied to the **inverting** (-) **input**

- The non-inverting input (+) is grounded

- The resistor  $R_f$  is the **feedback resistor**. It is connected from the output to the negative (inverting) input. This is *negative feedback*.

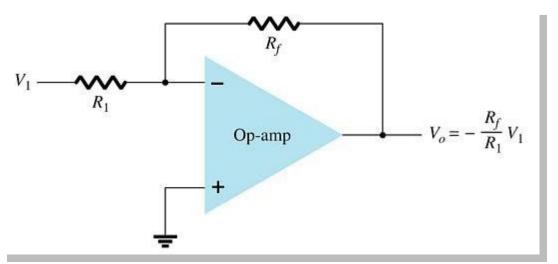

Inverting Op-Amp Gain

# **Inverting Op-Amp Gain**

Gain can be determined from external resistors: R<sub>f</sub> and R<sub>1</sub>

$$A_{v} = \frac{V_{o}}{V_{i}} = \frac{R_{f}}{R_{1}}$$

Unity gain—voltage gain is 1

$$R_{f} = R_{1}$$

$$A_{v} = \frac{-R_{f}}{R_{1}} = -1$$

The negative sign denotes a 180° phase shift between input and output.

Constant Gain—R<sub>f</sub> is a multiple of R<sub>1</sub>

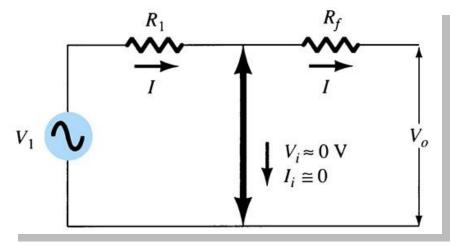

#### Virtual Ground Ground

An understanding of the concept of virtual ground provides a better understanding of how an opamp operates.

The *non-inverting* input pin is at ground. *The inverting* input pin is also at 0 V for an AC signal.

The op-amp has such high input impedance that even with a high gain there is no current from inverting input pin, therefore there is no voltage from inverting pin to ground—all of the current is through R<sub>f</sub>.

**Practical Op-Amp Circuits**

### **Practical Op-Amp Circuits**

Inverting amplifier Noninverting amplifier Unity follower Summing amplifier Integrator Differentiator

# Week - 12

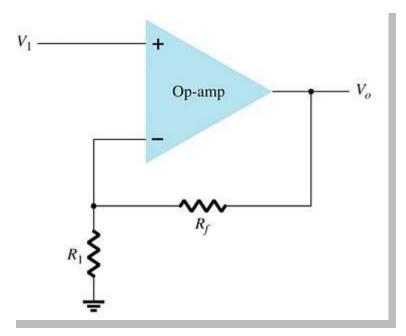

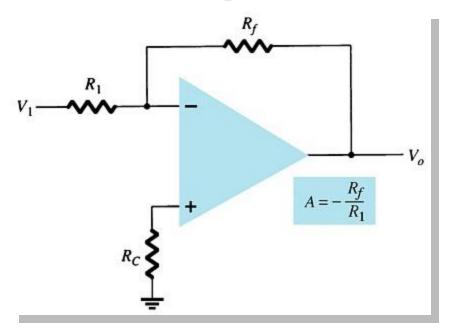

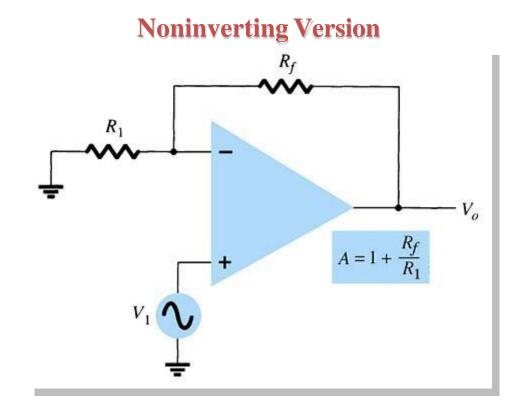

#### Inverting/Noninverting Op-Amps

### **Inverting/Noninverting Op-Amps**

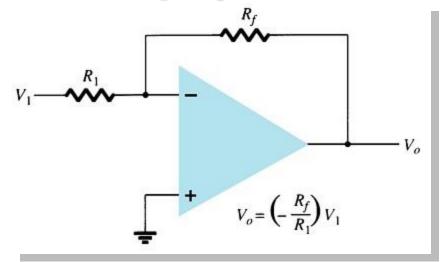

#### **Inverting Amplifier**

$$\mathbf{V_0} = \frac{-\mathbf{R_f}}{\mathbf{R_1}}\mathbf{V_1}$$

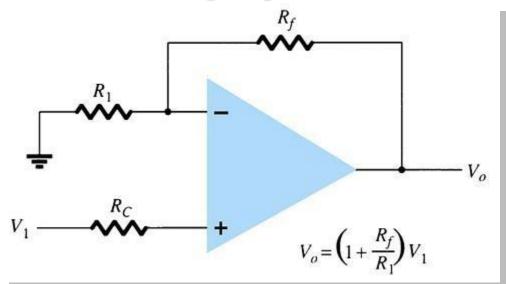

**Noninverting Amplifier**

$$\mathbf{V_0} = (1 + \frac{\mathbf{R_f}}{\mathbf{R_1}})\mathbf{V_1}$$

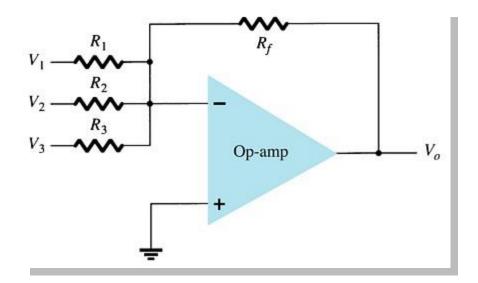

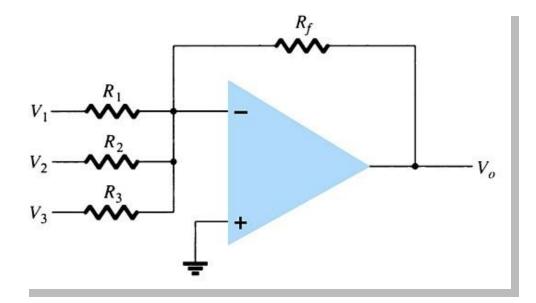

# Summing Amplifier Summing Amplifier

Because the op-amp has a high input impedance, the multiple inputs are treated as separate inputs.

$$\mathbf{V_0} = -\left(\frac{\mathbf{R_f}}{\mathbf{R_1}}\mathbf{V_1} + \frac{\mathbf{R_f}}{\mathbf{R_2}}\mathbf{V_2} + \frac{\mathbf{R_f}}{\mathbf{R_3}}\mathbf{V_3}\right)$$

Integrator

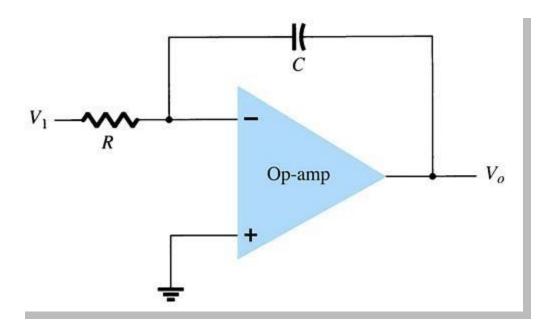

### Integrator

The output is the integral of the input. Integration is the operation of summing the area under a waveform or curve over a period of time. This circuit is useful in lowpass filter circuits and sensor conditioning circuits.

$$\mathbf{v_0}\left(t\right) = -\frac{1}{\mathbf{RC}}\int \mathbf{v_1}(t)dt$$

#### Differentiator

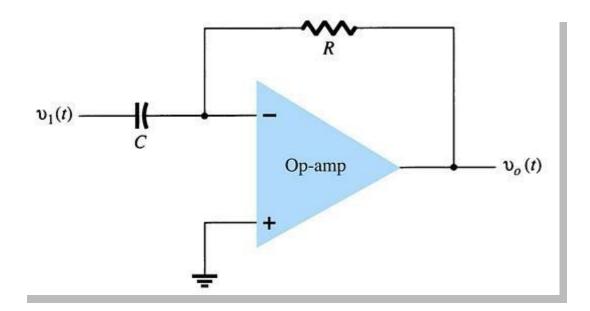

### Differentiator

The differentiator takes the derivative of the input. This circuit is useful in high-pass filter circuits.

$$\mathbf{v_0}\left(t\right) = -\mathbf{R}\mathbf{C}\frac{\mathbf{d}\mathbf{v_1}(t)}{\mathbf{d}t}$$

#### Op-Amp Specifications—DC Offset Parameters Op-Amp Specifications—DC Offset Parameters

Even when the input voltage is zero, there can be an output offset. The following can cause this offset:

- Input offset voltage

- Input offset current

- Input offset voltage *and* input offset current

- Input bias current

If there is a difference between the dc bias currents for the same applied input, then this also causes an output offset voltage:

- The input offset Current  $(I_{IO})$  is specified in the specifications for the op-amp.

- The effect on the output can be calculated using:

$$V_{o(offsetdue to I_{IO})} = I_{IO}R_{f}$$

# Week - 13

# Total Offset Due to V<sub>IO</sub> and I<sub>IO</sub> V<sub>IO</sub> and I<sub>IO</sub>

Op-amps may have an output offset voltage due to both factors  $V_{IO}$  and  $I_{IO}$ . The total output offset voltage will be the sum of the effects of both:

$V_0$  (offset) =  $V_0$  (offset due to  $V_{IO}$ ) +  $V_0$  (offset due to  $I_{IO}$ )

A parameter that is related to input offset current  $(I_{IO})$  is called input bias current  $(I_{IB})$

The separate input bias currents are:

$$I_{IB}^{-} = I_{IB} - \frac{I_{IO}}{2} \qquad \qquad I_{IB}^{+} = I_{IB} + \frac{I_{IO}}{2}$$

The total input bias current is the average:

$$\mathbf{I_{IB}} = \frac{\mathbf{I_{IB}^-} + \mathbf{I_{IB}^+}}{2}$$

**Frequency Parameters**

**Frequency Parameters**

An op-amp is a wide-bandwidth amplifier. The following affect the bandwidth of the op-amp:

- Gain

- Slew rate

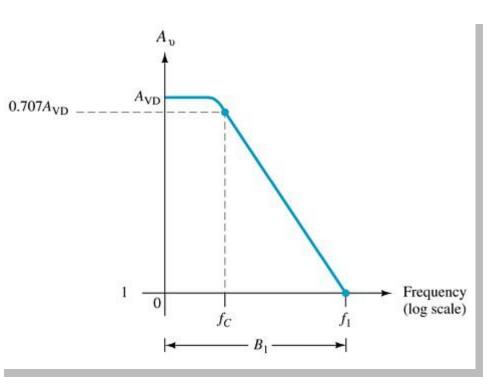

#### Gain and Bandwidth

### **Gain and Bandwidth**

The op-amp's high frequency response is limited by internal circuitry. The plot shown is for an open loop gain ( $A_{OL}$  or  $A_{VD}$ ). This means that the op-amp is operating at the highest possible gain with no feedback resistor.

In the open loop, the op-amp has a narrow bandwidth. The bandwidth widens in closedloop operation, but then the gain is lower.

Slew Rate (SR)

**Slew Rate (SR)**

**Slew rate (SR)** is the maximum rate at which an op-amp can change output without distortion.

$$\mathbf{SR} = \frac{\Delta \mathbf{V}_{\mathbf{o}}}{\Delta t} \quad (\mathbf{in} \, \mathbf{V}/\mu \mathbf{s})$$

The SR rating is given in the specification sheets as V/μs rating.

# Week - 14

Maximum Signal Frequency

**Maximum Signal Frequency**

The slew rate determines the highest frequency of the op-amp without distortion.

$$\mathbf{f} \leq rac{\mathbf{SR}}{2\pi \mathbf{V_p}}$$

#### where $V_P$ is the peak voltage

#### General Op-Amp Specifications

# **General Op-Amp Specifications**

**Other ratings for op-amp found on specification sheets are:**

- Absolute Ratings

- Electrical Characteristics

- Performance

# **Absolute Ratings**

These are common maximum ratings for the op-amp.

| Absolute                   | Maximum          |  |  |

|----------------------------|------------------|--|--|

| Ratings                    |                  |  |  |

| Supply voltage             | 6 22 V           |  |  |

| Internal power dissipation | 500 mW<br>6 30 V |  |  |

| Differential input voltage |                  |  |  |

| Input voltage              | 6 15 V           |  |  |

## **Electrical Characteristics**

| Characteristic                                      | MIN | TYP | MAX | Unit |

|-----------------------------------------------------|-----|-----|-----|------|

| V <sub>10</sub> Input offset voltage                |     | 1   | 6   | mV   |

| I <sub>IO</sub> Input offset current                |     | 20  | 200 | nA   |

| I <sub>IB</sub> Input bias current                  |     | 80  | 500 | nA   |

| V <sub>ICR</sub> Common-mode input voltage range    | ±12 | ±13 |     | v    |

| V <sub>OM</sub> Maximum peak output voltage swing   | ±12 | ±14 |     | v    |

| AvD Large-signal differential voltage amplification | 20  | 200 |     | V/mV |

| r <sub>i</sub> Input resistance                     | 0.3 | 2   |     | MΩ   |

| r <sub>o</sub> Output resistance                    |     | 75  |     | Ω    |

| C <sub>i</sub> Input capacitance                    |     | 1.4 |     | pF   |

| CMRR Common-mode rejection ratio                    | 70  | 90  |     | dB   |

| I <sub>CC</sub> Supply current                      |     | 1.7 | 2.8 | mA   |

| $P_D$ Total power dissipation                       |     | 50  | 85  | mW   |

Note: These ratings are for specific circuit conditions, and they often include minimum, maximum and typical values.

One rating that is unique to op-amps is CMRR or **common-mode** rejection ratio.

Because the op-amp has two inputs that are opposite in phase (inverting input and the non-inverting input) any signal that is common to both inputs will be cancelled.

**Op-amp CMRR is a measure of the ability to cancel out common-mode signals.**

# **Op-Amp Applications**

Constant-gain multiplier Voltage summing Voltage buffer Controlled sources Instrumentation circuits Active filters

## **Constant-Gain Amplifier**

#### **Inverting Version**

more...

## **Constant-Gain Amplifier**

### **Multiple-Stage Gains**

#### The total gain (3-stages) is given by:

$$\mathbf{A} = \mathbf{A}_1 \mathbf{A}_2 \mathbf{A}_3$$

or

$$\mathbf{A} = \left(\mathbf{1} + \frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}_{\mathbf{1}}}\right) \left(-\frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}\mathbf{2}}\right) \left(-\frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}\mathbf{3}}\right)$$

## **Voltage Summing**

The output is the sum of individual signals times the gain:

$$\mathbf{V}_{\mathbf{0}} = -\left(\frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}_{1}}\mathbf{V}_{1} + \frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}_{2}}\mathbf{V}_{2} + \frac{\mathbf{R}_{\mathbf{f}}}{\mathbf{R}_{3}}\mathbf{V}_{3}\right)$$

[Formula 14.3]

# Week - 15

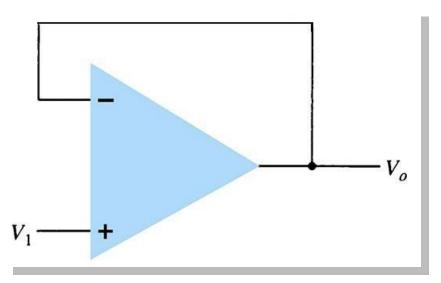

### **Voltage Buffer**

Any amplifier with no gain or loss is called a **unity gain amplifier**.

The advantages of using a unity gain amplifier:

- Very high input impedance

- Very low output impedance

Realistically these circuits are designed using equal resistors  $(R_1 = R_f)$  to avoid problems with offset voltages.

### **Controlled Sources**

Voltage-controlled voltage source Voltage-controlled current source Current-controlled voltage source Current-controlled current source

# **Voltage-Controlled Voltage Source**

The output voltage is the gain times the input voltage. What makes an op-amp different from other amplifiers is its impedance characteristics and gain calculations that depend solely on external resistors.

#### **Noninverting Amplifier Version**

# **Voltage-Controlled Voltage Source**

The output voltage is the gain times the input voltage. What makes an op-amp different from other amplifiers is its impedance characteristics and gain calculations that depend solely on external resistors.

#### **Inverting Amplifier Version**

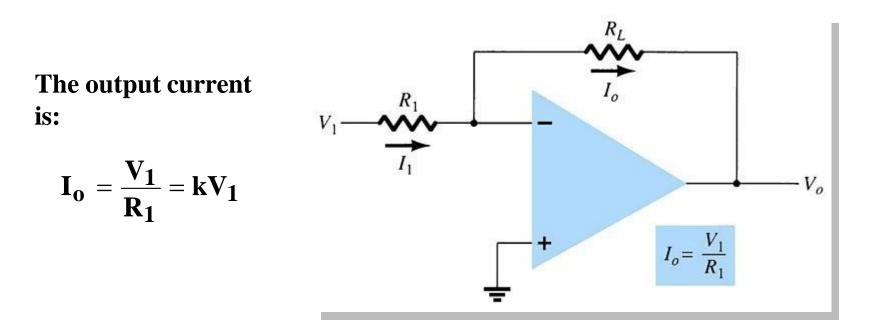

## **Voltage-Controlled Current Source**

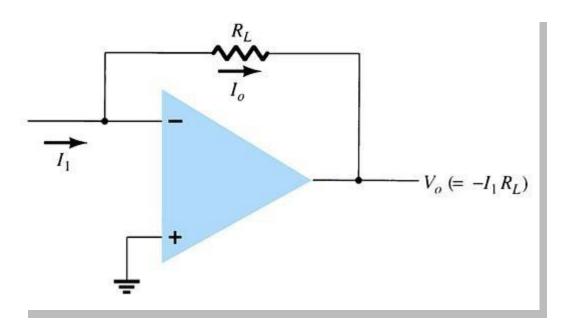

# **Current-Controlled Voltage Source**

This is simply another way of applying the op-amp operation. Whether the input is a current determined by  $V_{in}/R_1$  or as  $I_1$ :

$$\mathbf{V_{out}} = \frac{-\mathbf{R_f}}{\mathbf{R_1}} \mathbf{V_{in}}$$

or

$$\mathbf{V}_{\mathrm{out}} = -\mathbf{I}_{1}\mathbf{R}_{\mathrm{L}}$$

## **Active Filters**

Adding capacitors to op-amp circuits provides external control of the cutoff frequencies. The op-amp active filter provides controllable cutoff frequencies and controllable gain.

- Low-pass filter

- High-pass filter

- Bandpass filter

# Week - 16

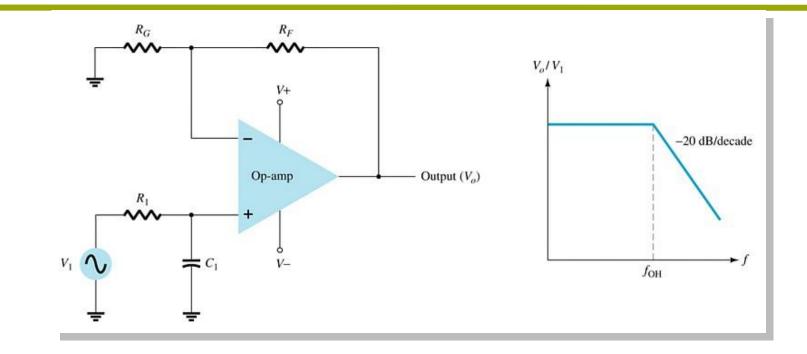

### **Low-Pass Filter—First-Order**

The upper cutoff frequency and voltage gain are given by:

$$f_{OH} = \frac{1}{2\pi R_1 C_1}$$

$A_v = 1 + \frac{R_f}{R_1}$

14 9

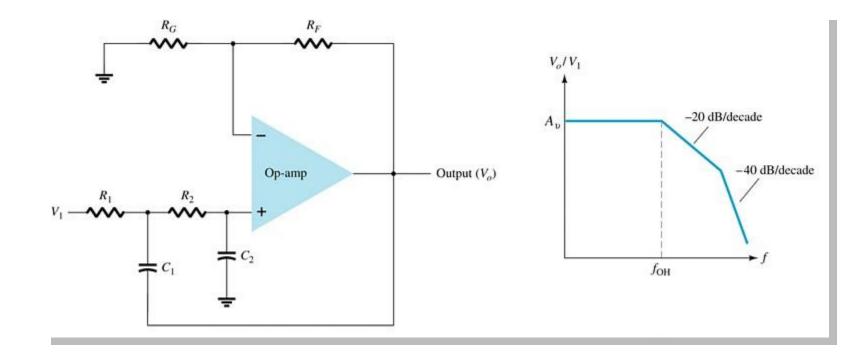

### Low-Pass Filter—Second-Order

The roll-off can be made steeper by adding more RC networks.

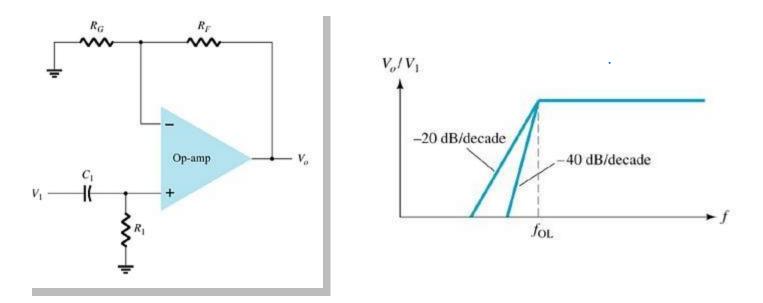

## **High-Pass Filter**

The cutoff frequency is determined by:

$$\mathbf{f_{OL}} = \frac{1}{2\pi \mathbf{R}_1 \mathbf{C}_1}$$

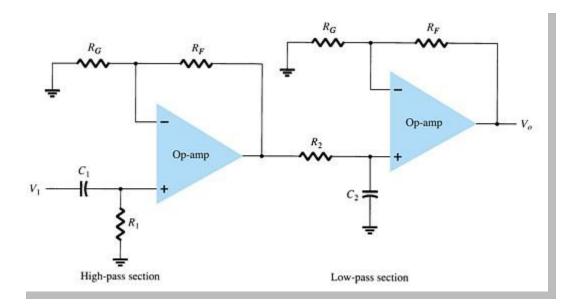

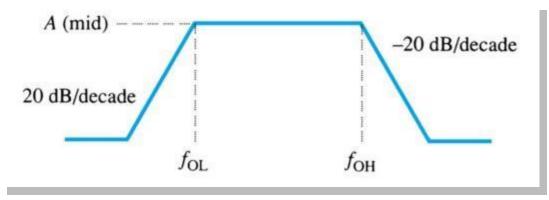

# **Bandpass Filter**

There are two cutoff frequencies: upper and lower. They can be calculated using the same low-pass cutoff and highpass cutoff frequency formulas in the appropriate sections.

# Week - 17

Mathematical Problem Solving (Will be Discussed in Class)

Presentation on Selected Topics